20分でわかる不要輻射対策

以下の文面はある機会に作成したものですが公益性の高い内容が含まれているので切り出して公開することにしました。

輻射の発生から対策の手がかり、現実的な運用まで参考になりそうなことを書きます。かなり実践寄りの内容になりますので、短めにまとめています(20分で読めるかどうかはその人次第)電磁気学の理論的な細かいところを知りたい方は是非専門書をあたって下さい。

私の電磁気学のベースの知識の大体は大学で使ったこの教科書でした。

ちなみに私の不要輻射対策の実務経験としては某大手企業時代のものが概ねベースになっています。(何度も電波暗室に篭りきりになる日々を過ごしたものです。。。)電源回路も自社製であったり、基板構成も後付けの建て増しになっている製品も多く、不要輻射対策としてはかなり厄介な部類の製品で経験を積ませてもらったと思っています。

とりあえず輻射について

『不要輻射』は別の言い方では『非意図的放射』とも言いますが、要するに出すつもりじゃなかった電波が出てる、という話です。

じゃあどういうところから出るかというと「電子回路の至る所」から多かれ少なかれ出てます。とはいえ電流がきれいに流れている系では輻射はほとんど発生しません。ここできれいに流れてるとはキレイに行って帰ってきてるという意味です。

さて、いかなる信号も電源から供給された電流を何かしらの形に変換してどこかに送り出し、離れた場所でキャッチされたら(ここで信号として読み取られる)その電流はまた別の経路を通って電源へ戻るという系で成立します。

この系の選択(どの経路を流れるか)は基本的にインピーダンスが低いところが選択されます。(ここら辺の根っこは量子論ですね。興味のある人は勉強してみると面白いですよ)でも一般的な基板ではそんなにキレイに電流が行ったりきたりできなくて(遠回りさせられたり、行き止まりで反射したり)電流密度に偏りが発生します。

ちなみにシリコンバレーにいたときにNVIDIAのレイアウト設計者と一緒に仕事したことがあり彼の設計を見ましたが、よく一般的な基板で見られる縦(90度)でも横(0度)でも斜め(45度)でもない微妙な角度の配線や緩やかなカーブでの配線などを使いこなしていました。電流密度の偏りを最小限にし、無駄なL成分や反射を作り出さないための設計的配慮ですね。

電流密度が偏ると一部の電荷がキレイに電源に戻ることができず、行き場を求めて飛び出します。ざっくりで言うとこれが不要輻射の元です。飛び出した電荷は帰り道を求めます。インピーダンスの低い経路で。電源の負極側に対して最もインピーダンスが低い箇所として期待されるのは通常GNDです。なので電流密度の偏りがある近辺にGNDがあるとそちらに飛んでいき、結果として輻射はとても小さいレベルで片付きます。

でもGNDの電源までのインピーダンスが期待するほど低くなかったり、近くに有効なGNDがなかったりすると電気力線はそのままぐるーっと出ていくことになり、電界の発生、つまり不要輻射が観測されます。そうならないようにGNDに対してよくやるのが

・GNDにVIAを打ちまくる

・GNDの面積を広くする

・内層をベタGNDにする

・高速信号の両側にGNDを配置する

というような手法です。これらはざっくり言うと全てインピーダンスを低くして電流をスッキリ返すための方策です。

さて、とりあえず輻射について言えることは

・全体から万遍なく出るわけではなくどこか特定箇所から突出して出ている(「吹いてる」とよく言う)

・電流密度の偏りはあらゆる条件の影響を受けるので正直読みづらい

対策の手がかり

不要輻射対策としてやれることは、どれだけ時代が変わろうとAIとビッグデータの時代になろうとシンギュラリティが来ようと正直あまり変わりません。

・元発を叩く

・電源GND対策を強化する

・輻射は出る前提で臭いものに蓋をする

元発(げんぱつ)を叩く

『元発=元となる発信器なりクロック』を叩くという発想です。これは極めて根本的な対策なので、もしこれが上手くできたら対策が完璧に終了します。

叩くというのは具体的には

・高調波を減らす

・配線、GNDを見直す

という考え方です。

矩形波に近づけば近づくほど信号には高調波が出ます。メインのクロックが10MHzなのに20MHzとか30MHzで不要輻射で落ちたりすることがよくあります。これは高調波のせいです。一般に周波数は高くなれば高くなるほど対策が難しくなることが多いので周波数は低いに越したことがありません。したがって波形を許容範囲内で鈍らせることは一つの有効な対策になり得ます。

これと似たようなことはインピーダンス不整合で信号の反射(リンギングなど)が起きているときなどにも発生します。

また、高調波が残っていると、電流密度分布は周波数依存性があるため(各種インピーダンスは周波数特性を持つため)「3次高調波を叩いたら5次が出た」などというモグラ叩き状態に陥るのも不要輻射対策あるあるです。

対策の具体的アイディア

・クロックや高速信号にRC(もしくはLC)を挿入する

・クロックや高速信号にダンピング抵抗もしくはフェライトビーズを入れる(反射防止)

製品を開発するときにはよく『クロック表』を作ります。元発となる水晶やPLLの周波数、通信用に使用しているクロックなどをまとめておくわけです。それを実際に対策に取り組むときの手がかりとします。

一般によくあるのは

・USB(480MHz, 12MHzとか)

・SoCの発信器(数10MHz)

・SDIO(~200MHzとか)

・オーディオのMCLK(24.576MHzとか)

とかですかね。

ちなみにこういう時は「外部に信号として出ているもの」と限定して考える方が好ましいです。何故かと言うと、それは仮にそのクロックが直接シリコンから吹いている場合は内部でしか対策が取れないのと、恐らくノイズは電源GND経由で外部に出るので叩くべき箇所はそちらになるからです。

発信器系

発信器のような箇所はおそらく回路的にはとてもシンプルです。従って気にすることは

・パターンが効率よく直近で接続されているか

・信号がビアを通して他のレイヤに行ったり来たりしていないか

このくらいです。つまりこのようなケースでできることはあまり多くはありません。

また生成されたクロックが仮に長旅をさせられているようなケースでは、よく内層に入れることをやります。GNDで挟み込むことでノイズ的に強くしようというよくある対策です。若干これは賛否あるところで、表面に出てれば対策が可能(ダンピング抵抗つけるとかC付けてフィルタにするとか)という考え方もありっちゃありだと私は個人的に思います。

通信系

通信系のクロックについて上記で触れましたが、もし輻射が出ていた場合にしんどいのがUSBでしょうね。

というのもUSBは通信性能の担保のためにアイパターンはキレイに維持したいです。そうすると信号を安易に鈍らせることはできないから(一番簡単な対策がボツ)です。

逆にUSBの通信そのものがノイジーでそこから吹いているようなケースもあると思います。そのような場合はほとんど反射が根本原因だと思いますが、反射を抑制することが「波形がキレイになって通信エラーが減る」「不要輻射が下がる」という一挙両得に結びつきます。例えば差動インピーダンスをTDRなどを用いてチェックしてみればどこで反射が起きているかがわかるかも知れません。

通信系というのは出元も行き先も一緒の複数の信号で構成されていることが極めて多いと思います。そうすると信号は大抵並行して通ることになります。一般に並行して通っている信号にはノイズの飛びつきが起きやすいです。例えばアナログ信号(音声など)とクロックが並行して通っているせいでノイズが乗ってトラブルになることなどがあります。それと同じですね。ある程度警戒すべき高速信号が頭の中にあれば、それとノイズに弱い信号は極力遠ざける配慮、もしそれが難しい場合はRやCが後で挿入できるように基板を作っておく配慮などがあると好ましいです。

電源GND対策の強化

考えるべきことは「電源や信号で発生しているノイズを如何に穏便にGNDに返すか」です。

パスコンの配置、定数を見直す

すでに例示したようなGND強化策に加えて『パスコンの配置、定数を見直す』というのもある種のGND強化策です。コンデンサのインピーダンスは周波数特性があり、基本的に小さい定数であれば高周波を通し、大きい定数ではあまり通しません。前者はAC的なノイズ低減に役立ち、後者はDC的なノイズ低減に役立つという大雑把な役割分担です。

不要輻射でNGな帯域がわかりきっているのであれば、そこに特化して「GNDにスムーズに帰るように」と定数を変更するのは効果がある時があります。インピーダンスを変えれば電流密度分布が変わるからです。

例えばよくMCUには同じ電位にぶら下がっているパスコンが複数あったりします。そういうパスコンの役割はざっくり2つで、ひとつはDC的に電源供給をサポートすること、もうひとつは高周波ノイズに対する電源のインピーダンスを下げることです。この手のパスコンはすぐに大きめのGNDに繋がっていることが多いので、もしこの電源がノイジーな場合はパスコンの定数調整もしくは追加によってノイズレベルが下がることがあります。

電源GNDに直列で何某

ノイズは電流です。なので抵抗で消費させて熱にしてしまえばノイズそのものがなくなります。とはいえDCや通信で使っている周波数で働くインピーダンス成分を迂闊に増やすと、動作に問題が発生することがあります。もしそのノイズの周波数が通信の周波数よりも遥かに高ければ、その帯域をバッツリ落とすフィルタ、もしくはフェライトビーズなどを電源GNDにシリーズ(直列)で入れればとても効果が得やすいです。

またこの考え方を適応する際はノイズがその電源系の外部から来ているのか内部から発生しているのかも気にする必要があります。もし外部からであれば、仮にノイズの周波数と通信の周波数が被っている場合もまずはバッツリ遮断してしまって、電源系の内部でデカップリングコンデンサの定数の調整により短期的な電力供給をカバーするような機構を作ることができます。めでたしめでたし。なおその際もコンデンサはインピーダンスという周波数依存の内部抵抗を持った電池みたいなものだと考えれば良いです。つまり短期少量供給であれば小さい定数の方が適していて、中長期の大量供給であれば大きい定数が適していると言えます。あとはさじ加減はカット&トライです。

ACアダプタやUSBのBUS Power、スイッチング電源のノイズなどが原因となっている場合はそこで叩けばかなり落ちることが期待できます。主に機器の入り口でどうするか、という視点で考えるのが好ましいです。

一方、電源ICの側から見るとそれぞれのICがノイズに汚れていてそれを電源IC側に返す、というのは最大限避けるべきです。具体的にはLCフィルタなりで落とすのが単純な解です。そして「どこが汚れやすい電源だろうか?」と考えるとよく思い当たるのはCPUやメモリバス、DSP、FPGA、GPUなどです。

臭いものに蓋をする

最終手段。事後対策についてです。

シールドする

多くの通信モジュールなどで取られている方法です。当然ノイズも低減させますし、改変が困難であることという電波法上の『モジュール』の要件を簡単に満たすことができるので多くのモジュールはシールドが付いていますね。

板金はもし入れることができれば最強のノイズ対策部品です。ただし、その板金をGNDに落とすことはくれぐれも忘れずに。電位的に浮いている板金は新たなアンテナもしくはリフレクターとして働きます。リフレクターとして巧みに使っている事例の代表格が八木アンテナです。

ケーブルをツイストペアにする

ツイストペアが有効なのはどこかで発生したノイズがケーブルに乗っている場合です。 ケーブルは基本的にとても優秀なアンテナです。ケーブルに乗ったノイズはどこかに行って大抵悪さをしますので取り除いておくべきです。ツイストペアの効果に関する詳しい説明はネットにいくらでも転がっているのでそちらに譲ります。要するにノイズによってケーブル上に発生する起電力を近距離でそれぞれ逆向きにすることで相互に消し合う構造にするっていうコロンブスの卵。

その他の悪あがき

* 悪さをしている信号線にフェライトコアを巻く

* 配線を変える(板金があればそれにくっつけて固定する)

* 電波吸収体をぺたぺた貼る

* 汚いGNDをアースに近いポイントに電気的につなげる

ここら辺の話はがっつり効くことが多いですが、手加工が増えたり対策部品が高かったり、中長期的な対応としては好ましくはないことが多いので正直悩みどころです。

対策の開始にやるべきこと

上記までの対策のアイディア等々を踏まえて、対策開始にやるべきことはNGになっている周波数の元発は何か? を極力明確に明らかにすることです。似たような周波数のクロックが複数箇所に存在するユニットなどは特に要注意です。

ステップは

1. 基板上に存在する周波数を列挙してあたりをつける

2. ソフト的に止めることが可能であったらクロックを止めてみる(クロックダウンするでも良い)

3. 止めれない場合は部品を外すなどで回路を遮断する

なおこの過程で便利なのがポータブルの簡易スペアナです。私が使っているのはこれですが(安いけど案外使える)

発生箇所を見極めるときのノウハウ①「バラす」

クロックを止めることが容易ではない部品を使っている場合は、全部が動作した状態で見ざるを得なかったりすることは考えられます。小型機器だったり基板同士の距離が近かったりすると、もう発生箇所はよくわかりません。

そういうときはケーブルを引き伸ばして基板同士を物理的に離すというやり方が有効です。筐体から出してしまって、基板を机の上に並べて、その上をスペアナであたるわけです。当然厳密な状態の確保はできていないのであくまで電波が吹いている箇所を突き止めるためだけのやり方です。

発生箇所を見極めるときのノウハウ②「スペアナで『直接』あたる」

スペアナはアンテナを着けるものと一般に理解されています。それはそのとおりなのですが、実は違う使い方もできます。プローブを着けてしまうのです(普通に見れます)プローブによって部品を直接あたったりGNDを直接あたったりすれば、かなり詳細に電流密度の乱れを見ることができます。ただ重要な注意点は以下です。

・プローブは高周波対応の同軸ケーブルを用いたものを使うこと

・端子で直接あたらずに、端子の先に、例えば1pFのリードのセラコンなどをつけてそれ経由で部品にあたること(DCが入るとスペアナぶっ壊れるので)

これはちょっと上級者向けかも知れませんね。

発生箇所を見極めるときのノウハウ③「手で触る」

人体は結構優秀なノイズ対策部品でして(容量も持ってるし多くの場合で接地されてるし)手で触ることによって輻射が下がる様子が観測できる時があります。そういう箇所が発見できたらそこは対策箇所です。

同じような話でケーブルを触るだけで下がったり、特定の2箇所を同時に触ることで下がったりすることがあります。これらは対策の上で大きなヒントになります。

発生箇所を見極めるときの注意点

* 電波には偏波があります。アンテナの向きは常に変えて試さないと見落とすことがあります

* 1GHz以下は水平方向以外の放射(床面への放射)も気にする必要があります。逆に1GHz以上は水平方向以外は気にしなくて良いです

* 電波的に静かな環境を作ること

どこから電波が吹いているかがわかった後で考えること

電波が出ている箇所がわかったら「じゃあ対策!」とその前に少し慎重に考えるべきことがあります。

吹いている箇所と原発の位置

まずとても重要なポイントは吹いている箇所と原発の位置が一致しているかどうかです。

もし一致している場合、取れる対策はかなり限られます。例えばプロセッサの内部クロックがプロセッサから出ている場合、できることはシールド(金属 or 電波吸収体)くらいしかないことがよくあります。

とはいえ最近のCPUやGPUではそのようなケースはあまり見ないので(メーカーが対策済み)基本的に、このケースではできることが非常に限られる、ということだけ押さえておけばと思います。

通信経路か電源GNDか

通信経路の場合は割とシメたものです。例えばFFCの配線から電波が吹いていることはよくあります。その場合はシールドとして銅箔テープを巻くだけでかなり下がったりします。もし基板上の配線の場合はGNDに落とした銅箔や電波吸収シートを貼るだけでピタリと治ったりします。

これらのケースの場合は当座の対策は割と簡単ですが、加工が手間であったりコストがかかったりするので、基本的にはいずれ基板を直すべきだと思います。例えばケーブル配線であればコネクタ周辺にRCもしくはLCのフィルタを組んだりコモンモードチョークなどの対策部品を挿入することでスッキリ消えることが考えられますし、基板上の配線の場合はガードGNDや内層GNDを適切にすることで解消する可能性があります。

電源GND系から吹いている時が最も厄介です。

どうやら広範囲(複数箇所)から出ていて電源やGNDのプレーンが犯人

プレーンから出ている時は本当に厄介です。理由は以下

・どこかを叩いたら大抵別の場所が出る(もぐらたたき状態。対策に時間がかかる)

・検討がここまで来ているケースは「元発は叩けなかった」加えて「どこか特定の叩きやすい場所から出てなかった」というパターンだと考えられる。その場合はもはや「散らす」か「塞ぐ」しか選択肢がない

「散らす」というのはノイズを極力分散させるということです。すでにここまでに述べてきたような電源、GNDを極力きれいに電流が流れるようなタイトな接続の構造にするということです。あまり一発で片付く魔法は存在しなくて地道な作業になります。(もぐらたたき)

もぐらたたきにならないように古来から行われているのがシミュレーションです。

村田のFemtetなんかは結構な化物ソリューションのクセにとても価格的にリーズナブルだと思います。

https://www.muratasoftware.com/

「塞ぐ」というのはこれも既に触れた「臭いものに蓋」です。補足は特にありません。

また、ちょっと変化球としては「わざと偏りを作ってそこを叩く」という手もあります。

具体的には電源GNDを高周波的に切り離しまくるということです。そうすることでノイズの行き場所は限定できるのでそこで叩く、という発想です。しかしながらそれぞれの電源GNDは弱くなるため小型基板でこれをやるとそのせいで打てる手がなくなって詰んだりもします。なかなか難しい。

総論

不要輻射対策はステージ、日程、予算感などによって制約を受けることがよくあります。時間と予算に余裕があれば基板を作り直すのが正道です。その段でシミュレーションにかけるのも悪くはありません(本当は最初からやれば理想的だけどリスクが顕現してないとなかなかその手間は取れないものなので)もしリスクを前もって予見していたら(以前てこずったモデルの基板やモジュールの設計をそのまま引き継いでいる、とか)思いつく限り0Ω抵抗をやたらめったら入れておく、というのは私もやったことが何度かあります。いざ輻射NGとなったらそこを対策部品に変えるわけです。

ということで、不要輻射対策で頭を抱えるのは上記のような余裕や事前の策がない場合がほとんどだということになります(そりゃそうだ)

となると「とりあえずペタペタ貼りまくって出たとこ勝負だ!」となりがちですが(私もやりはじめの頃にそういうことは何度もありました)ここまでに記述したような原理や全体像を知っているといくつも役に立つことがあるように思います。

・電波が出てる場所にきちんと貼る(プレーンか?ケーブルか?)

・ノイズを熱にするかGNDに戻すかによって貼るものを変える

・GND拡大によるシールディングを目指す場合は変に電流密度が高まる場所を作らないように注意する

などなど。対策作業自体はある程度手探りになりますが、頭にこういうことが入っていて手探りするのと暗中模索では大違いです。

おまけ

LかRか

直列に挿入してノイズを抑制するとしたら選択肢に上がるのはL(=フェライトビーズ等)かR(=抵抗)です。

Lは周波数特性があるため「ある特定周波数を落とす」という目的に対してとてもフィットしています。Rはそれ自体がDC的な電圧低下の元になることがあり得るため、一見使い方は難しいように見えます。

しかし、Lを直列に使うときには意図するしないに関わらず、パスコンのあるなしに関わらず、LCフィルタが構成されます。それはLが挿入された先のICの入力容量、基板の容量、もろもろのCが必ずくっついているからです。LCフィルタの周波数特性には必ず共振特性が見られます。

これはある箇所でフィルタがノイズを強める方に働くことを意味します(直列共振)ある箇所では弱めたつもりが別の箇所で強くなる点が出てしまうということです。

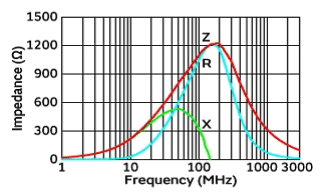

この影響を和らげるための工夫がフェライトビーズです。例えば以下の村田のアイテム

https://www.murata.com/ja-jp/api/pdfdownloadapi?cate=cgsubChipFerriBead&partno=BLM03AG102SN1%23

ではインピーダンス特性がこのようになります。

この周波数を共振周波数近辺に持っていけば(そういうフェライトビーズを選択すれば)複合的な効果でターゲット周波数をキレイに落とすことができます。きちんと考えてきちんと落とす。

逆にRはとってもシンプルに考えて良いのでカットオフ周波数だけ計算してRCフィルタを構成すればすこぶる素直にノイズは下がります。ただ素直が取り合えなので特殊なことはできません(例えば特定の場所にピークを持ってくるような)

利点欠点見極めて使いこなすようにして下さい。

ロットで順次対応

対策を生産ロットで順次やっていくのはよくある話です。簡単に想像がつくと思いますが「1stロットは来月なので打てる対策は電波吸収体のみ。だけど2ndロットまでは半年くらいあるからきちんと対策が取れる」というような状況があります。

その場合はできれば2チーム(担当者2人、かも知れなけど)を作って当たれると良いかも知れません(何せやることが違うので)短期的なもぐらたたきは力技の体力勝負です。一方長期的な対策は計算(シミュレーション含む)と試作のやり直しによって手数よりもきちんと考えた末に一発 or 二発で解決するというアプローチです。

両者を時系列も配慮して上手く組み合わせることが開発現場のノウハウと言えると思います。